# ACB-BF592 ユーザーズマニュアル 第 5 版

金子システム株式会社

# ご注意

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。 当社製品のご購入およびご使用にあたりましては、当社ホームページを通じて公開される情報を参 照ください。

- 2. 当社から提供する情報の正確性と信頼性には万全を尽くしていますが、誤りがないことを保証する ものではありません。当社はその使用に対する責任を一切負いません。その使用によって第三者の 特許権、著作権その他知的財産が侵害された場合でも、同様に責任を負いません。

- 3. 本資料は、当社の書面による事前の明示同意がない限り、いかなる形式でも複製できません。

- 4. 当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

# 目次

| 1 | はじ  | .めに          | 3 |

|---|-----|--------------|---|

|   |     | パッケージ内容      |   |

|   |     | ·ドウェア・リファレンス |   |

|   |     | 製品外観         |   |

|   |     | ブロック図        |   |

|   |     | 外形寸法         |   |

|   |     | 電気特性         |   |

|   | 2.5 | DIP スイッチの設定  | 6 |

|   | 2.6 | コネクタ仕様       | 7 |

|   | 2.7 | JTAG ヘッダ     | 9 |

| 3 | 更新  | 「履歴          | 9 |

# 1 はじめに

このたびは当社製品をご購入いただき、ありがとうございます。

本製品は、アナログ・デバイセズ社 DSP である Blackfin ADSP-BF592 を使用した CPU ボードです。本製品 ACB-BF592 の特徴は以下の通りです。

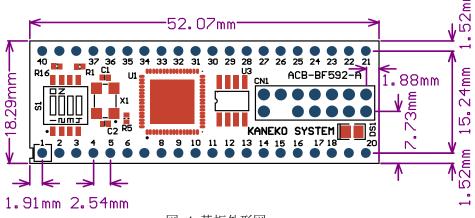

- 52.07mm×18.29mm と小型で、600mil 40 ピン DIP IC と同一サイズです

- ブレッドボードに挿入でき、実験に最適です

- Blackfin の動作に必要な電源は基板にて生成するため、3.3V を供給すれば動作いたします

- DIP スイッチにより、ブートモードが切換えできるため、ご都合に合わせたブートが指定可能です

- SPI フラッシュメモリ搭載なので、外部データの保存も可能です

また、ADSP-BF592プロセッサの特徴は以下の通りです。

- 最大 400MHz コアクロックで動作し、2 個の MAC(積和演算器)により、800MMACs(メガ積和演算/秒)のパフォーマンスに達します

- 遅延なしで動作可能な L1 SRAM を 68k バイト内蔵

- C ランタイムライブラリ、VDK RTOS コードが書かれた L1 ROM を内蔵

- 省電力

- 2個のSPI、2個のSPORT、1個のUART、1個のPPI

- 9個のペリフェラル DMA チャンネルと、2個のメモリ間 DMA チャンネル

- 9×9mmのLFCSPパッケージ

詳細は、アナログ・デバイセズ社の ADSP-BF592 のサイトを参照ください。

http://www.analog.com/jp/processors-dsp/blackfin/adsp-bf592/processors/product.html 関連する技術資料は、以下を参照ください。

$\frac{http://www.analog.com/jp/processors-dsp/blackfin/adsp-bf592/processors/technical-documentation/index.html$

● 回路図やサンプルプログラムは、以下のサイトを参照ください。 http://kaneko-sys.co.jp/support/

# 1.1 パッケージ内容

ACB-BF592 のパッケージには、以下が含まれます。

表 1 パッケージ内容

| 内容            | 数量 |

|---------------|----|

| ACB-BF592 ボード | 1枚 |

| 20×1 列 ピンヘッダ  | 2個 |

| 13 ピンヘッダ      | 1個 |

# 2 ハードウェア・リファレンス

# 2.1 製品外観

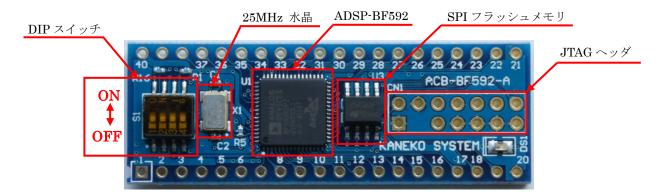

図 1 表面写真

図 2 裏面写真

ご使用前に、DIPスイッチの保護シートをはがしてください。

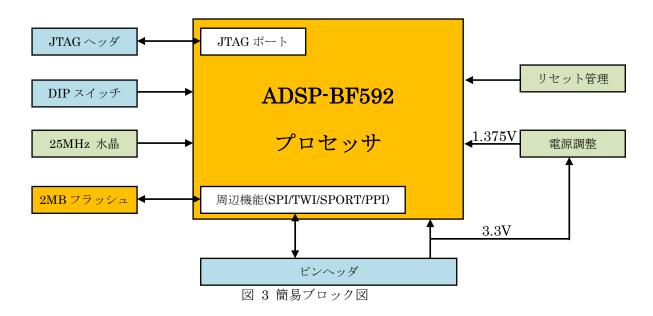

# 2.2 ブロック図

ここでは、ACB-BF592ボード上のプロセッサの構成を説明します。

ACB-BF592 は、ADSP-BF592 Blackfin プロセッサを中心に、動作に最低限必要となる以下の機能で構成されています。

- JTAG ヘッダ

- DIP スイッチ(ブートモード、フラッシュメモリのライトプロテクトを設定)

- 25MHz 水晶

- 2MB SPI フラッシュメモリ

- 1.375V リニアレギュレータ

- リセット管理(リセットスーパーバイザ)

#### 2.3 外形寸法

図 4 基板外形図

# 2.4 電気特性

表 2 電気特性

| 項目            | 条件            | 記号      | min  | typ  | max  |

|---------------|---------------|---------|------|------|------|

| 供給電圧          | _             | VCC_3V3 | 3.0V | 3.3V | 3.6V |

|               | CCLK:400MHz   |         | _    | 78mA |      |

|               | SCLK:100MHz   |         |      |      |      |

|               | CCLK:350MHx   |         | _    | 70mA |      |

|               | SCLK: 87.5MHz |         |      |      |      |

| 3.3V 供給時の消費電流 | CCLK:300MHz   |         | _    | 62mA |      |

| (実測・参考値)      | SCLK:75MHz    | ICC     |      |      |      |

| (天側・参与框)      | CCLK:250MHx   |         | _    | 54mA |      |

|               | SCLK:62.5MHz  |         |      |      |      |

|               | CCLK:200MHz   |         | _    | 45mA |      |

|               | SCLK:50MHz    |         |      |      |      |

|               | CCLK:150MHx   |         | _    | 38mA |      |

|               | SCLK:37.5MHz  |         |      |      |      |

# 電流測定条件

- ・Visual DSP++から JTAG-ICE を使ってプログラムを実行

- ・SPI フラッシュからデータを連続リード

- ・PLL の設定以外プログラムは同一

消費電流は参考値です。プログラムや使用するペリフェラル、動作環境によって異なりますので、供給側の出力電流は余裕をもった設計にしてください。

# 2.5 DIP スイッチの設定

SPI フラッシュメモリのライトプロテクトおよび、ADSP-BF592 のブートモードの設定を行います。

表 3 DIP スイッチ機能表

| 番号 | 操作  | 説明                                |

|----|-----|-----------------------------------|

| 1  | ON  | SPI フラッシュメモリ(U3) をライトプロテクトに設定します。 |

|    | OFF | SPI フラッシュメモリ(U3) のライトプロテクトを解除します。 |

| 2  | ON  | BMODE2 ピンの論理をLに設定します。             |

|    | OFF | BMODE2 ピンの論理を H に設定します。           |

| 3  | ON  | BMODE1 ピンの論理をLに設定します。             |

|    | OFF | BMODE1 ピンの論理を H に設定します。           |

| 4  | ON  | BMODE0 ピンの論理をLに設定します。             |

|    | OFF | BMODE0 ピンの論理を H に設定します。           |

各ブートモードに対応したスイッチ2~4の設定は以下の通りです。

ブートモードの詳細は、アナログ・デバイセズ社「ADSP-BF59x Blackfin Processor Hardware Reference」を参照ください。

表 4 ブートモードと DIP スイッチの対応

| ブートモード                      | スイッチ |     | F   | 備考                  |

|-----------------------------|------|-----|-----|---------------------|

| 000                         | 2    | 3   | 4   |                     |

| Idle/No Boot                | ON   | ON  | ON  |                     |

| 001                         |      |     |     | 設定しないでください          |

| Reserved                    |      |     |     |                     |

| 010                         | 2    | 3   | 4   |                     |

| SPI1 master boot using PG11 | ON   | OFF | ON  |                     |

| 011                         | 2    | 3   | 4   |                     |

| SPI slave boot              | ON   | OFF | OFF |                     |

| 100                         | 2    | 3   | 4   | 基板搭載の SPI フラッシュメモリか |

| SPI0 master boot using PF8  | OFF  | ON  | ON  | らブート                |

| 101                         | 2    | 3   | 4   |                     |

| Boot from PPI port          | OFF  | ON  | OFF |                     |

| 110                         | 2    | 3   | 4   |                     |

| Boot from UART host device  | OFF  | OFF | ON  |                     |

# 2.6 コネクタ仕様

- ※ 各表の入出力は、ADSP-BF592 からみたもので、信号名の最後に # が付く名前は、負 論理 (Low アクティブ) であることを示します。

- ※ 各ピンの詳細は、アナログ・デバイセズ社「ADSP-BF59x Blackfin Processor Hardware Reference」を参照ください。

表 5 コネクタ仕様

| ピン番号 | 信号名      | 入出力 | 説明                            |

|------|----------|-----|-------------------------------|

| 1    | EXT_WAKE | 出力  | Wake Up 出力                    |

| 2    | PPI_CLK  | 入力  | PPI クロック入力                    |

|      |          |     | $100$ k $\Omega$ でプルダウンされています |

| 3    | I2C_SCL  | 入出力 | I2C クロック                      |

| 4    | I2C_SDA  | 入出力 | I2C データ                       |

| 5    | PF0      | 入出力 | PF0/DR1SEC/PPI_D8/WAKEN1      |

| 6    | PF1      | 入出力 | PF1/DR1PRI/PPI_D9             |

| 7    | PF2      | 入出力 | PF2/RSCLK1/PPI_D10            |

| 8    | PF3      | 入出力 | PF3/RFS1/PPI_D11              |

| 9  | PF4       | 入出力 | PF4/DT1SEC/PPI_D12             |

|----|-----------|-----|--------------------------------|

| 10 | PF5       | 入出力 | PF5/DT1PRI/PPI_D13             |

| 11 | PF6       | 入出力 | PF6/TSCLK1/PPI_D14             |

| 12 | PF7       | 入出力 | PF7/TFS1/PPI_D15               |

| 13 | PF9       | 入出力 | PF9/TMR0/PPI_FS1/SPI0_SSEL3    |

| 14 | PF10      | 入出力 | PF10/TMR1/PPI_FS2              |

| 15 | PF11      | 入出力 | PF11/UA_TX/SPI0_SSEL4          |

| 16 | PF12      | 入出力 | PF12/UA_RX/SPI0_SSEL7/TACI2-1  |

| 17 | SPI0_MOSI | 出力  | SPI0_MOSI                      |

| 18 | SPI0_MISO | 入力  | SPI0_MISO                      |

| 19 | SPI0_SCK  | 入出力 | SPI0_SCK                       |

| 20 | GND       | _   | 電源グラウンド                        |

| 21 | GND       | _   | 電源グラウンド                        |

| 22 | PG0       | 入出力 | PG0/DR0SEC/SPI0_SSEL1/SPI0_SS  |

| 23 | PG1       | 入出力 | PG1/DR0PRI/SPI1_SSEL1/WAKEN3   |

| 24 | PG2       | 入出力 | PG2/RSCLK0/SPI0_SSEL5          |

| 25 | PG3       | 入出力 | PG3/RFS0/PPI_FS3               |

| 26 | PG4       | 入出力 | PG4(HWAIT)/DT0SEC/SPI0_SSEL6   |

| 27 | PG5       | 入出力 | PG5/DT0PRI/SPI1_SSEL6          |

| 28 | PG6       | 入出力 | PG6/TSCLK0                     |

| 29 | PG7       | 入出力 | PG7/TFS0/SPI1_SSEL7            |

| 30 | PG8       | 入出力 | PG8/SPI1_SCK/PPI_D0            |

| 31 | PG9       | 入出力 | PG9/SPI1_MOSI/PPI_D1           |

| 32 | PG10      | 入出力 | PG10/SPI1_MISO/PPI_D2          |

| 33 | PG11      | 入出力 | PG11/SPI1_SSEL5/PPI_D3         |

| 34 | PG12      | 入出力 | PG12/SPI1_SSEL2/PPI_D4/WAKEN2  |

| 35 | PG13      | 入出力 | PG13/SPI1_SSEL1/SPI1_SS/PPI_D5 |

| 36 | PG14      | 入出力 | PG14/SPI1_SSEL4/PPI_D6/TACLK1  |

| 37 | PG15      | 入出力 | PG15/SPI1_SSEL6/PPI_D7/TACLK2  |

| 38 | NMI#      | 入力  | NMI 入力                         |

|    |           |     | 4.7k の抵抗でプルアップされています           |

| 39 | RESET_IN# | 入力  | リセット入力                         |

| 40 | VCC_3V3   | _   | 3.3V 電源                        |

|    |           |     |                                |

# 2.7 JTAG ヘッダ

表 6 JTAG ピンヘッダ

| ピン番号 | 信号名     | ピン番号 | 信号名   |

|------|---------|------|-------|

| 1    | GND     | 2    | EMU#  |

| 3    | (KEY)   | 4    | GND   |

| 5    | VCC_3V3 | 6    | TMS   |

| 7    | GND     | 8    | TCK   |

| 9    | GND     | 10   | TRST# |

| 11   | GND     | 12   | TDI   |

| 13   | GND     | 14   | TDO   |

JTAG ヘッダには、以下の JTAG-ICE を使用することが可能です。

表 7 JTAG-ICE

| 製品名            | 備考                                                              |

|----------------|-----------------------------------------------------------------|

| Analog Devices | http://www.analog.com/jp/processors-dsp/blackfin/usb-emulator   |

| ADZS-HPUSB-ICE | bf/processors/product.html                                      |

| Analog Devices | http://www.analog.com/jp/processors-dsp/blackfin/usb-emulator   |

| ADZS-USB-ICE   | bf/processors/product.html                                      |

| Analog Devices | http://www.analog.com/jp/processors-dsp/blackfin/emulator-100/  |

| ADZS-100B-ICE  | processors/product.html                                         |

| gnICE+         | http://docs.blackfin.uclinux.org/doku.php?id=hw:jtag:gnice-plus |

# 3 更新履歴

| 版   | 更新日        | 更新内容                           |

|-----|------------|--------------------------------|

| 第1版 | 2012/01/23 | 初版発行                           |

| 第2版 | 2012/04/09 | P8-9 表 4 21~40番ピンの番号が逆順だったため修正 |

| 第3版 | 2012/05/28 | P4 サポートページの案内を追加               |

|     |            | P6 VDDINT 電圧値変更(1.375V)        |

| 第4版 | 2013/01/17 | P7 電気特性追加                      |

| 第5版 | 2013/01/23 | P5 基板外形図更新                     |